С каждым днем увеличивается объем цифровой информации, которую необходимо хранить на запоминающих устройствах. Назначение памяти может быть очень разнообразным: оперативная память, постоянная память или же память, предназначенная для хранения значений в LUT (LookUp Table) в функциональных блоках ПЛИC (программируемая логическая интегральная схема). Но во всех видах памяти важными характеристиками являются быстродействие и степень интеграции.

В настоящее время подавляющее число ячеек памяти создается на основе транзисторов. Постоянное усовершенствование технологии позволяет уменьшать их размеры, тем самым увеличивая количество ячеек на единицу поверхности, но с каждым новым увеличением интеграции происходит значительное усложнение технологии. Решением данной проблемы может стать использование мемристоров, которые занимают меньшую площадь, имеют достаточно высокое быстродействие, а также энергонезависимы (при отключении питания мемристор сохраняет свое состояние).

Мемристор – один из четырех базовых пассивных элементов, появление которого было предсказано в 1971 году профессором Леоном Чуа [1]. В 2008 году HP labs объявили о получении прототипа мемристора [3]. Особенность этого элемента заключается в способности изменять свое сопротивление при приложении напряжения, а также сохранять свое состояние при отключении питания [4]. Такое свойство мемристора позволяет применять его в многоуровневой логике, нейронных сетях, а также в ячейках памяти.

Мемристор представляет собой структуру металл-диэлектрик-металл. При создании используются различные материалы, но чаще всего применяются оксид титана и платина. Рабочим телом является оксид титана, платина выполняет роль двух терминалов, к которым прикладывается напряжение [5]. Структура имеет размеры 40×40 нм, что по сравнению с транзистором в 5–6 раз меньше (при 32 нм технологии).

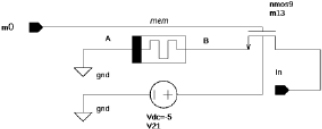

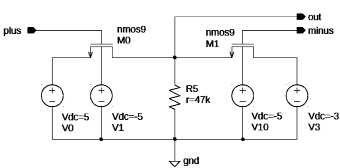

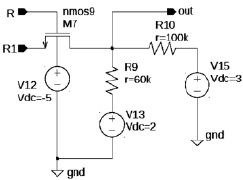

Для моделирования ячейки памяти в САПР Cadence была разработана схемотехническая модель мемристора. На ее основе разработана ячейка памяти, которую можно разделить на три составляющие части: ячейка памяти (рис. 1), схема записи (рис. 2) и схема считывания

(рис. 3).

Рис. 1. Ячейка памяти

Pис. 2. Схема записи

Рис. 3. Схема считывания

Ячейка памяти состоит из транзистора и мемристора. Транзистор выполняет роль ключа, который открывает доступ к мемристору. Особенность заключается в том, что к подложке транзистора подключает-

ся –3 В, а на затвор подается +5 и –5 В. Это необходимо для того, чтобы транзистор пропускал положительное и отрицательное напряжение. Благодаря этому на один из терминалов мемристора подается +2 и –2 В (в то время как второй терминал подключен к земле), и соответственно мемристор может перейти в нужное

состояние.

Для перезаписи мемристора необходима схема записи, которая представлена на рис. 2. Она состоит из двух транзисторов и двух источников напряжения. На подложки транзистора так же подается напряжение в –3 В. Когда на терминал Plus подается +5 В, транзистор открывается. Напряжение в +3 В, генерируемое источником напряжения, проходя через открытый транзистор, подается на сток транзистора в ячейке памяти, и если он открыт, +3 В прикладывается к мемристору, переводя его в ON состояние (состояние с низким сопротивлением, равным 1 кОм). Когда же на терминал Minus подается +5 В, на сток транзистора в ячейке памяти подается –3 В, и мемристор соответственно может переключиться в OFF состояние (состояние с низким сопротивлением, равным 100 кОм).

Чтобы определить состояние мемристора, можно использовать схему считывания, которая работает по принципу делителя напряжения. Напряжение делится между резистором в 100 кОм и мемристором. Резистор номиналом 60 кОм необходим для получения нужных значений напряжения при разных логических уровнях. В результате при сопротивлении на мемристоре 2 кОм на выход приходит 0,2 В, при 100 кОм, соответственно, 1 В.

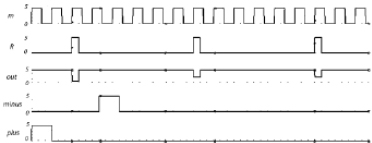

Предложенная принципиальная схема была промоделирована в САПР Cadence, в результате чего была получена временная диаграмма представленная на рис. 4. На ней можно увидеть, что при одновременном приложении напряжения +5 В на транзистор открывающий доступ к мемритору (/m) и транзистор, позволяющий приложить +3 В (/plus), мемристор переходит в On состояние, и при последующим считывании (приложении +5 В к терминалу /R) на выход (/out) приходит 0,2 В. При приложении +5 В к терминалу minus, мемристор переходит соответственно в Off состоянии, и на выход, при чтении, приходит 1 В.

Рис. 4. Временная диаграмма ячейки памяти

Преимущество представленной схемы заключается в использовании одинаковых транзисторов, что позволяет сократить до минимума количество производственных этапов. Также малый размер ячейки дает возможность создавать память с очень высокой плотностью.

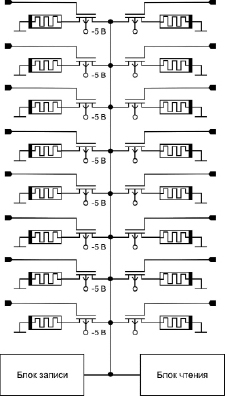

Используя предложенное схемотехническое решение, можно спроектировать LUT (LookUp Table) для функциональных блоков ПЛИC. Особенность данной схемы заключается в возможности использовать одну схему считывания и записи на несколько ячеек памяти. Количество ячеек ограничивается только паразитной емкостью проводников, которая может повлиять на скорость переключения мемристоров. Однако значение данной емкости сравнительно не большое, поэтому можно использовать одну схему считывания и записи на 16 ячеек памяти (рис. 5).

Рис. 5. Схема LUT для функциональных блоков ПЛИС

LUT в функциональных блоках ПЛИС, созданных на основе мемристоров, имеют в 20–25 раз меньшую площадь по сравнению с ячейками памяти на транзисторах. Также мемристоры энергонезависимы, что позволяет более эффективно использовать их в теневой памяти. Скорость чтения составляет 10 нс [2], что также удовлетворяет требованиям памяти в функциональных блоках ПЛИС.

Работа выполнена при финансовой поддержке Министерства образования и науки Российской Федерации (гос. соглашение №14.A18.21.0107) в рамках ФЦП «Научные и научно-педагогические кадры инновационной России» на

2009–2013 годы.

Рецензенты:

Агеев О.А., д.т.н., профессор, директор Научно-образовательного центра «Нанотехнологии» Южного федерального университета, г. Таганрог;

Рындин Е.А., д.т.н., профессор, ведущий научный сотрудник Южного научного центра Российской академии наук (ЮНЦ РАН), г. Ростов-на-Дону.

Работа поступила в редакцию 16.10.2012.