Scientific journal

Fundamental research

ISSN 1812-7339

"Перечень" ВАК

ИФ РИНЦ = 1,798

METHOD OF LAYOUT SUPERDENSE NON-VOLATILE MEMORY DESIGNING BASED ON MULTILAYER MEMRISTORS’ ARRAYS

Повышение интеграции микроэлектронных устройств, в частности, вычислительных систем со встроенными блоками памяти возможно только при увеличении числа элементов на единицу площади кристалла. Поэтому, если нет возможности сократить технологические нормы, остается один естественный выход – повысить число слоев с активными и пассивными элементами [3].

Традиционные КМОП-схемы, состоящие из нескольких совмещенных кристаллов, имеют ряд недостатков, в частности, они относительно дороги, а также у них слишком низкая плотность соединений из-за ограничений на точность совмещения отдельных кристаллов (по сравнению с точностью совмещения фотолитографических масок) [4].

Показатель производительности системы-на-кристалле зависит не только от скорости вычислений, плотности компонентов, энергоэффективности, надежности и т.д., но и от функциональности. На сегодня наметился общемировой отраслевой тренд (который по прогнозам окончательно оформится до 2019 года [3]) на добавление в системы-на-кристалле все новых и новых функций. Например, к традиционному КМОП кристаллу добавляют сенсоры, микроэлектромеханические компоненты, фотовольтаику, аналоговые сверхвысокочастотные модули и т.п. Эта общая тенденция, тем не менее, сталкивается с рядом технологических проблем по интеграции различных материалов в единый рабочий механизм. В частности, кремниевые транзисторы с высокой подвижностью носителей в КМОП-логике очень не просто совместить с традиционными модулями памяти. Однако большинство разработчиков микроэлектронных приборов достаточно успешно идут по пути объемной интеграции кристаллов [4].

Энергонезависимая память является продуктом совмещения ряда технологий, которые, как правило, развиваются в отдельных, относительно независимых областях их приложений. Например, требования к энергонезависимой памяти варьируются в зависимости от приложений, скажем, для радиочастотных меток требуется не очень быстрая и малая по объему (единицы Кбайт) память, а для больших высокопроизводительных чипов соответственно быстрая и большого объема (десятки Гбайт).

Применение мемристоров в качестве элементов энергонезависимой памяти выгодно отличает их от Flash-технологии тем, что для Flash-ячейки требуется как минимум один транзистор с дополнительным нитридным слоем. В мемристорной памяти активным элементом является только двухполюсник с обслуживающей общей схемой не сложнее, чем у традиционной памяти. Мемристор ‒ это двухполюсник, меняющий свое сопротивление в зависимости от общего количества заряда, который проходит через него [1]. Данный прибор состоит из полупроводниковой оксидной тонкой пленки, в которой под воздействием тока перемещаются ионы кислорода и меняют общую проводимость. Форма мемристора на кристалле – это, фактически, квадрат с минимальными для применяемой технологии сторонами. Изготовление мемристорной матрицы предполагает применение технологических процессов, полностью совместимых с КМОП-технологией. Дополнительно к традиционным КМОП-процессам добавляются только процессы нанесения платины (или эквивалента) и оксида металла, например, титана.

Структура многослойной

мемристорной памяти

Одной из основных проблем для любой высокоинтегрированной вычислительной системы является поддержание на достаточно высоком уровне пропускной способности с низкой задержкой обмена данными между слоями без излишних затрат площади. Одно из решений данной задачи описано в [5], где используется гибридная структура – элементы КМОП с матрицей мемристоров, расположенной над ними. В такой архитектуре применен интерфейс доступа к каждому элементу памяти на основе адреса, состоящего из логических 4-х частей.

В работе [5] предложен подход построения сверхплотного варианта энергонезависимой памяти, по сути объединяющий несколько слоев мемристорных матриц в объеме, т.е. лежащих один на другом для экономии площади. Число мемристоров на единицу площади, которые могут быть адресованы в такой архитектуре, на два порядка больше, чем транзисторов КМОП-схемы.

Нами предлагается архитектура, представляющая собой гибридную схему (технология КМОП + мемристоры), в котором мемристорная память располагается непосредственно над КМОП-элементами, реализующие основные вычислительные процессы и управление памятью. Запоминающие элементы образованы в виде межслойных переходов в местах взаимно-перпендикулярного пересечения гребенки металлических проводников, т.е. в виде регулярной прямоугольной матрицы [2]. Для управления данной мемристорной матрицей необходимы КМОП-схемы для селекции, записи и чтения индивидуальных битов. Эти управляющие схемы относительно малы по сравнению даже с Flash-памятью.

Такое построение интегральных схем может быть применено для встроенных блоков памяти, теневой памяти программируемых логических интегральных схем (ПЛИС), синаптических сетей и др.

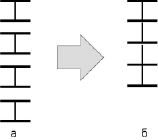

При применении описанного подхода предлагается отказаться от части слоев металлизации в мемристорной многослойной матрице, а также от транзисторов в ячейках, в качестве коммутационных элементов. Сокращение слоев достигается за счет объединения смежных слоев (рис. 1) и обращения полярностей мемристоров, через один в одной вертикали. Конечно, это накладывает дополнительные требования к применению особого алгоритма управления напряжением проводников для обеспечения четкой селекции конкретного элемента без влияния на соседние мемристоры.

Рис. 1. Схематичное изображение слоев металлизации и пересечений между ними (мемристоров) в блоке памяти одной и той же плотности:

а – в подходе из [5]; б – число необходимых слоев металла сокращено

по предложенному методу

Сокращение числа слоев металла в предложенных мемристорных матрицах составляет:

(M – 1)·(2M)·100 %,

где M – число слоев мемристоров, расположенных один над другим.

Для нашего примера на рис. 1 (M = 4) сокращение слоев металла достигает – 37,5 %.

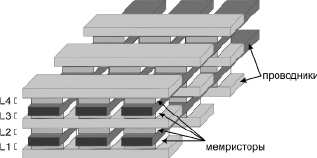

Иллюстрация описанного принципа редуцирования слоев в мемристорных матрицах без потери их функциональности приведена на рис. 2.

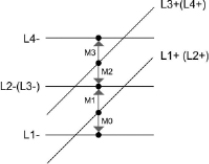

Если рассматривать отдельно каждую вертикаль из мемристоров, то ее электрическая схема будет выглядеть как представлено на рис. 3, на котором мемристоры показаны стрелками, отображающими их полярность.

Рис. 2. Объемный разрез фрагмента слоистых мемристорных матриц (M = 4)

Рис. 3. Схема одной вертикали в слоистой мемристорной матрице (при M = 4)

Числовые обозначения проводников (в именах L1–, L1+, L2+, L3– и т.д.) на рис. 3 введены для удобства адресации к конкретному слою мемристоров, а знаки + и – представляют относительную полярность прикладываемого напряжения.

Поскольку все мемристоры «вплетены» в регулярную матрицу, то для того чтобы считать или записать бит в отдельный двухполюсник, следует придерживаться следующего алгоритма подачи уровней напряжений на проводники матрицы:

– для записи «1» в мемристор, расположенный, например, на 1-м уровне (M0 на рис. 3), необходимо:

а) установить положительное напряжение на проводнике L1+;

б) установить отрицательное напряжение на проводнике L1–;

в) установить нулевое напряжение на всех остальных проводниках матрицы.

– для записи «0» в мемристор, расположенный, например, на 3-м уровне (M2 на рис. 3), необходимо:

а) установить положительное напряжение на проводнике L3–;

б) установить отрицательное напряжение на проводнике L3+;

в) установить нулевое напряжение на всех остальных проводниках матрицы.

Напряжения, подаваемые на проводники при селекции конкретного элемента, должны быть подобраны таким образом, чтобы не происходило потери запомненных состояний проводимости на соседних мемристорах. Другими словами, разность потенциалов между положительным и отрицательным уровнями может «переключить» мемристор, а разность между нулевым и положительным или отрицательным –нет. Конкретные цифры будут зависеть от технологии изготовления мем-

ристоров.

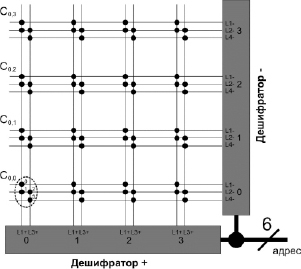

В целом организация блока памяти на примере для четырех слоев мемристоров и 6-разрядной адресации показана на рис. 4.

Рис. 4. Организация адресного пространства блока памяти на основе слоистых мемристорных матриц

Здесь применены два дешифратора, которые отвечают за установку положительных, отрицательных и нулевых уровней напряжения на проводниках многослойной мемристорной матрицы. На рис.4 пересечения матрицы, в которых находятся мемристоры, показаны черными точками с цифрами, представляющими номера слоев (M0, M1, M2 и M3).

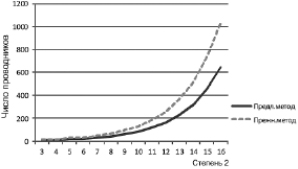

Сравнительный анализ количества проводников в блоке памяти при применении подхода из работы [5] и предложенного в статье метода показал, что происходит их сокращение примерно на 37 % для любых разрядностей. Зависимость абсолютных чисел приведена на рис. 5.

Рис. 5. Зависимость числа адресных проводников в блоке памяти от разрядности адреса

Выводы

Предложенный метод формирования многослойной мемристорной матрицы позволяет использовать его для разработки встраиваемых блоков энергонезависимой памяти или теневой памяти конфигурации ПЛИС. Сокращение числа слоев металлизации и адресных проводников матрицы по сравнению с аналогичным подходом составляет порядка 37 %.

Работа выполнена при финансовой поддержке Министерства образования и науки Российской Федерации (гос. соглашение № 14.A18.21.0107) в рамках ФЦП «Научные и научно-педагогические кадры инновационной России»

на 2009–2013 годы.

Рецензенты:

Агеев О.А., д.т.н., профессор, директор Научно-образовательного центра «Нанотехнологии» Южного федерального университета, г. Таганрог;

Рындин Е.А., д.т.н., профессор, ведущий научный сотрудник Южного научного центра Российской академии наук (ЮНЦ РАН), г. Ростов-на-Дону.

Работа поступила в редакцию 16.10.2012.

Библиографическая ссылка

Калашников Г.В., Ковалев А.В., Бирюков М.И. МЕТОД ПОСТРОЕНИЯ СВЕРХПЛОТНОЙ ТОПОЛОГИИ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ НА ОСНОВЕ МНОГОСЛОЙНЫХ МЕМРИСТОРНЫХ МАССИВОВ // Фундаментальные исследования. 2012. № 11-2. С. 397-401;URL: https://fundamental-research.ru/en/article/view?id=30545 (дата обращения: 30.04.2026).