Сегодняшнюю жизнь невозможно представить без вычислительных систем (ВС), скрытых в бытовой технике, измерительных приборах, телекоммуникациях и т.п. Особое место среди ВС занимают многопроцессорные системы (МПС), использующиеся, например, для научных исследований и расчетов, которые, как правило, требуют колоссального быстродействия и слаженной работы подсистемы «процессор ? память».

Целью данной статьи является разработка аппаратного буферного устройства (АБУ) памяти МПС с общей шиной, состоящей из 4 процессоров (ЦП). Разрабатываемое устройство предназначено для быстрого доступа к памяти. В результате использования данной разработки существенно снижается загрузка памяти, увеличивается пропускная способность подсистемы «процессор ? память» и повышается быстродействие МПС в целом.

Постановка задачи

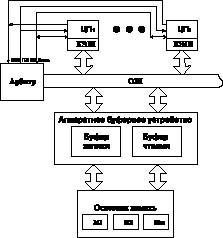

Имеется МПС, состоящая из 4 ЦП (рис. 1). Также имеется канал передачи, к которому подключены все ЦП ? общая шина (ОШ), в функции которой входит обмен данными между ЦП, оперативной памятью и внешними устройствами. В реальных МПС на занятие ОШ могут претендовать сразу несколько устройств, однако в каждый момент времени сделать это может только одно из них. Чтобы исключить конфликты, ОШ должна предусматривать определенные механизмы арбитража запросов и правила предоставления шины одному из запросивших устройств [1, 5].

ОШ представлена в соответствии со спецификацией AMBA (Advanced Microcontroller Bus Architecture) [6], разработанной как стандарт коммуникаций для высокопроизводительных систем-на-кристалле.

Рис. 1. Многопроцессорная система с аппаратным буферным устройством памяти

Стандарт АМВА, протокол и организация шины хорошо согласуются с проектированием синтезируемых, параметризуемых модулей и систем-на-кристалле на их основе. Стандарт шины АМВА включает в себя спецификации трех шин [2]:

? АНВ – Advanced High-performance Bus.

? ASB – Advanced System Bus.

? АРВ – Advanced Peripheral Bus.

В настоящее время коммуникационные системы на базе стандарта АМВА находят широкое применение в системах-на-кристалле аэрокосмического назначения. Например, шины АМВА используются для организации системы коммуникаций в системах-на-кристалле на процессорном ядре leon, организованном в соответствии с архитектурой sparc v8 [2]. Шина АМВА АНВ используется и в разрабатываемых отечественных системах-на-кристалле, например, в рамках проекта «Мультикор» [2].

Стандарт АМВА разработан для построения высокопроизводительных систем. Обмен данными в соответствии с этим стандартом осуществляется в синхронном режиме. В рамках стандарта предусмотрена поддержка пакетных передач и расщепленных транзакций (split transactions). В системе должно быть не более 16 ведущих устройств, число ведомых устройств не ограничено. Организация коммуникаций по шине осуществляется под управлением арбитра.

Для реализации АБУ использована шина AMBA АНВ [2], выступающая посредником между ЦП и памятью. При непрерывном выполнении операции (транзакции) записи или чтения памяти ОШ монопольно владеет один из ЦП системы до тех пор, пока операция не будет завершена. Таким образом, шина и ЦП находятся в режиме ожидания до тех пор, пока память не произведет физическую процедуру чтения или записи. В результате теряются циклы шины, которые могли быть использованы другими ЦП. Для уменьшения временных потерь и повышения пропускной способности ОШ необходимо, чтобы она поддерживала режимы расщепления транзакций чтения и буферизации транзакций записи.

Расщеплению подвергается операция чтения памяти, причем она делится на адресную транзакцию и транзакцию данных. При обращении к памяти ЦП выставляет на ОШ адрес, который сохраняется в АБУ, после чего ОШ освобождается, а ЦП переходит в режим ожидания. Процедура физического чтения происходит в памяти самостоятельно под управлением АБУ, которое по окончании процедуры физического чтения должно сигнализировать запрашивающий ЦП о готовности данных. В ответ ЦП вновь запрашивает ОШ и читает слово данных из АБУ [3, 4].

Буферизация транзакций записи заключается в том, что ЦП выставляет на шину адрес ячейки памяти и записываемые данные. Они сохраняются в регистрах АБУ, после чего ЦП освобождает ОШ, поскольку обратная реакция памяти в этом случае отсутствует. Процедура физической записи в память происходит под управлением АБУ [3, 4].

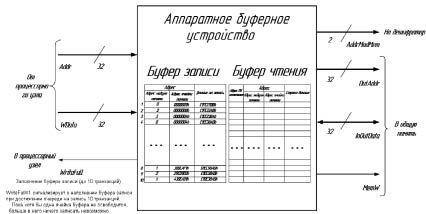

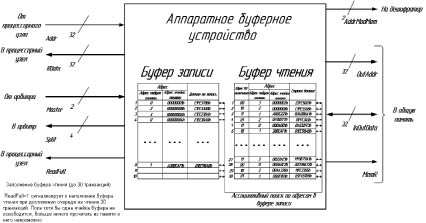

Из вышесказанного следует, что разрабатываемый блок должен быть снабжен двумя буферными устройствами для хранения транзакций чтения и записи (рис. 2). В свою очередь, буфер чтения имеет две части. Первая содержит регистры для хранения адреса ячейки памяти, в которую производится обращение, вторая – регистры для хранения выбранных из памяти данных. Буфер записи также состоит из двух частей. В первой хранятся адреса ячейки памяти, в которую производится обращение, во второй хранятся записываемые данные.

В работе используется архитектура МПС с однородным доступом к памяти – Uniform Memory Access (UMA). Для увеличения пропускной способности памяти она разбивается на ряд независимых модулей, каждый из которых имеет собственные схемы адресации и буферизации данных. При условии применения шины с расщеплением транзакций обеспечивается возможность доступа к памяти нескольких ЦП одновременно. Время доступа к данным из памяти не зависит ни от того, какой именно ЦП обращается к памяти, ни от того, какой именно чип памяти содержит нужные данные. При этом каждый ЦП может использовать свой собственный кэш [1].

а

б

Рис. 2. Структурная схема аппаратного буферного устройства памяти в режиме записи (а) и чтения (б)

Принцип действия устройства заключается в следующем. Предположим, что один или несколько ЦП одновременно сгенерировали транзакцию записи. Чтобы успешно ее реализовать, необходимо получить доступ к ОШ, для чего ЦП посылают сигналы запроса в арбитр, который, в свою очередь, проверяет, свободна ли ОШ в данный момент, и выбирает по некоторому правилу один из ЦП для осуществления операции. Если ОШ свободна, то ЦП захватывает ее. Далее происходит проверка на заполнение буфера записи, и если он полон, то ЦП переводится в режим ожидания. Если имеется хотя бы один свободный регистр в буфере записи, то ЦП помещает туда слово данных. Дальнейшая работа ЦП не зависит от результата записи, т.е. ему нет смысла дожидаться окончания записи, поэтому он освобождает шину.

В буфере записи может скопиться множество запросов, и возможна такая ситуация, когда запрос на чтение будет ссылаться на данные, уже находящиеся в АБУ, а не в памяти, таким образом, их можно прочитать напрямую из АБУ, а не из памяти, что существенно быстрее, чем обращение к памяти. Для быстрой реализации этой функции адресный буфер записи выполняется в виде ассоциативной памяти.

Процедура чтения с расщеплением транзакций допускает совмещение по времени сразу нескольких транзакций, формируемых разными ЦП. В начале операции чтения запрашивающий ЦП занимает шину, выставляет на нее адрес и сигнал чтения, которые фиксируются в буфере чтения. Эта транзакция выполняется быстро, поскольку буферы реализуются на аппаратных регистрах. После этой процедуры ЦП отключается от шины. Буферное устройство самостоятельно осуществляет процесс физического чтения данных из модуля памяти и сохранения результата в одном из регистров буфера чтения. В подходящий момент времени, когда шина свободна, данные возвращаются ЦП.

В системах с общей памятью все ЦП имеют равные возможности по доступу к единому адресному пространству. Единая память может быть построена как одноблочная или по модульному принципу, но обычно на практике встречается второй вариант [5]. С целью повышения быстродействия имеет смысл применить расслоение памяти по адресам на 4 модуля.

Далее рассмотрим варианты реализации алгоритма работы АБУ. Поделим подсистему «процессор ? память» на две подсистемы: «процессор ? АБУ» и «АБУ ? память». Соответственно представим два алгоритма работы устройства: со стороны ЦП и со стороны памяти.

Рассмотрим алгоритм функционирования подсистемы «процессор ? АБУ». Изначально ЦП должен проверить линию блокировки, определяющую, свободна или занята ОШ в данный момент времени, и гарантирующую монопольное владение ОШ одним из ЦП. Примем, что высокий потенциал на этой линии соответствует незанятости ОШ. Итак, ЦП, требующие ОШ, опрашивают линию блокировки, и если на ней обнаруживается высокий потенциал, то они посылают запросы в арбитр по индивидуальным линиям запроса. ЦП, имеющий наивысший приоритет, определяемый арбитром, получит сигнал подтверждения запроса. Этот является разрешающим для занятия ОШ. После захвата ЦП ОШ происходит выбор типа операции: чтение или запись. Если выбрана операция записи в буфер записи, то вначале он проверяется на наличие свободных ячеек, и в том случае, если он полон, ЦП переводится в «спящее» состояние, в котором находится до тех пор, пока не освободится хотя бы одна ячейка в буфере записи. Если же есть свободные ячейки, то происходит запись адреса и данных в буфер записи, после чего ЦП освобождает ОШ. Если выбрана операция чтения, то также вначале проверяется буфер чтения на наличие свободных ячеек, если таковых нет, ЦП также переводится в состояние ожидания, до тех пор пока не появятся свободные ячейки. Если свободные ячейки есть, то происходит запись адреса, по которому запросившему ЦП должны быть предоставлены данные для чтения. После процедуры физического чтения из памяти или ассоциативного поиска в буфере записи по указанному адресу будут считаны данные в буфер чтения. АБУ сигнализирует ЦП, которому предназначены выбранные данные, о готовности, и он считывает их из буфера чтения, после чего освобождает ОШ.

Теперь рассмотрим алгоритм функционирования подсистемы «АБУ ? память». Изначально производится выборка типа операции: запись или чтение. При операции записи происходит запрос j-го модуля памяти, в который будут записаны данные, переданные АБУ ЦП. Затем происходит проверка j-го модуля памяти на занятость: если он занят, то необходимо ожидание, если свободен, то происходит его занятие и запись данных по указанному адресу. Затем память освобождается и также освобождается одна ячейка буфера записи: СчБЗ: = СчБЗ – 1, где СчБЗ – счетчик (семафор) буфера записи (в данной статье принято, что СчБЗ = 10, т.е. емкость буфера записи равна 10 ячеек). При операции чтения происходит запрос k-го модуля памяти, из которого будут прочитаны данные в АБУ, для их последующей передачи соответствующему ЦП. Затем происходит проверка k-го модуля памяти на занятость: если он занят, то необходимо ожидание, если свободен, то происходит его занятие и чтение данных по указанному адресу. Затем прочитанные данные заносятся в ячейку буфера чтения: СчБЧт: = СчБЧт + 1, где СчБЧт – счетчик (семафор) буфера чтения (в данной статье принято, что СчБЧт = 30, т.е. емкость буфера чтения равна 30 ячеек). После этого модуль памяти освобождается, а АБУ сигнализирует запросивший i-й ЦП о готовности.

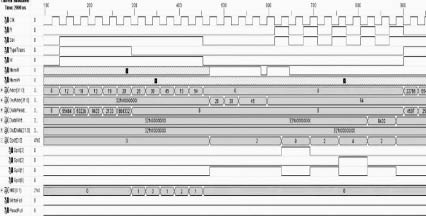

Рис. 3. Временные диаграммы работы аппаратного буферного устройства памяти