Устройства памяти считаются одним из основных компонентов современных систем на кристалле (СнК). Согласно оценкам экспертов ITRS (International Technology Roadmap for Semiconductors) встроенные устройства памяти занимают до 60 % площади всего кристалла [1]. Благодаря большой плотности размещения и значительной площади, занимаемой ими на кристалле, встроенные устройства памяти являются заметными источниками дефектов изготовления, снижающими процент выхода годных микросхем. Это приводит к необходимости пересмотра стратегий ремонта систем памяти [2, 5].

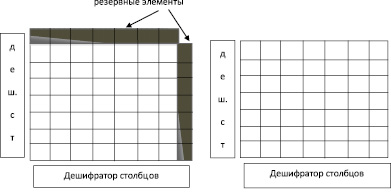

С целью ремонтирования устройств памяти и повышения процента выхода годной памяти (ВГД) в структуру памяти помещают резервные элементы, которые в случае необходимости должны заменять поврежденные элементы (рис. 1).

На рис. 1, а и б представлены, соответственно, структуры матрицы с возможностью ремонта и без. Как видно, устройство памяти с возможностью ремонта представлено двумя частями.

1. Функциональные ячейки.

2. Резервные или запасные ячейки, которые предназначены для ремонта памяти в случае отказов функциональных ячеек.

При обнаружении дефекта ячейка (строка и/или столбец), содержащая дефектный элемент, отключается от функциональной структуры памяти, а на ее место подключается строка/столбец из резерва.

Для эффективного ремонта современных систем памяти необходимо увеличить количество резервных элементов. В результате осложняется процесс анализа ремонта и структуры анализаторов. Таким образом, возникает необходимость создания оптимальных методов предварительного ремонта перед выполнением ремонта (анализа ремонта), методов проектирования встроенных анализаторов.

а б

Рис. 1. Устройство памяти с избыточными элементами

Цель работы: разработка методов проектирования встроенных в кристалл анализаторов ремонта памяти.

Анализ ремонта

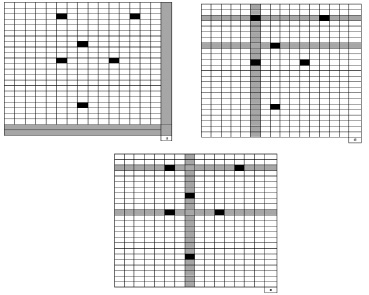

В ремонте систем памяти одной из наиболее актуальных задач является разработка методов предварительного анализа ремонта перед выполнением ремонта (анализ ремонта). Основная задача методов анализа ремонта – оптимальное покрытие дефектных элементов памяти минимальным количеством резервных элементов. Рассмотрим для примера матрицу памяти, изображенную на рис. 2, а, в которой имеются две резервные строки, один резервный столбец и шесть дефектных ячеек, обнаруженных в матрице.

Рис. 2. Пример покрытия дефектов

Использование простого линейного алгоритма замещения приводит к результату, изображенному на рис. 2, б, который, очевидно, не покрывает все дефекты. Оптимальный вариант замещения показан на рис. 2, в. В общем случае, нахождение оптимального варианта покрытия при наличии как резервных строк, так и резервных столбцов, математически называется проблемой NP-полноты, или, выражаясь более простым языком, это представляет собой проблему, сложность которой возрастает экспоненциально с ростом числа резервных элементов.

Анализ ремонта выполняется анализатором ремонта (BIRA-контроллера). На его долю обычно приходится основная часть дополнительного оборудования, следовательно, главное требование, которое к нему предъявляется, в дополнение к указанным функциям – компактность. С увеличением количества резервных элементов, однако, усложняются структуры встроенных анализаторов и увеличиваются их физические размеры. Таким образом, возникает необходимость создания новых оптимальных методов проектирования встроенных анализаторов.

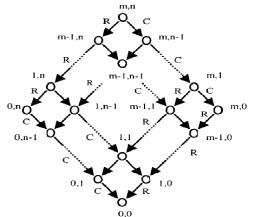

Алгоритмы анализа ремонта можно представить с помощью так называемой диаграммы потребления [3, 4]. Рассмотрим это на примере столбца M и строки N (рис. 3). Возможные варианты использования (потребления) резервных элементов можно рассмотреть на следующей диаграмме (рис. 3), где R(row) означает использование резервной строки, С (column) – колонки.

Эта диаграмма представляет собой граф, в котором произвольный маршрут, идущий от вершины (m, n) до вершины (0, 0), является покрытием, которое может решить проблему ремонта. Проблема в том, чтобы выяснить, какой маршрут отремонтирует все дефекты. Общее число возможных решений по ремонту может быть измерено по формуле для биномиальных коэффициентов:

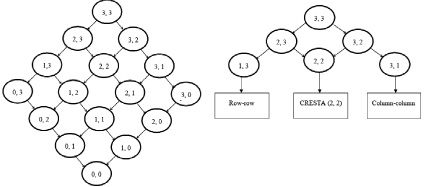

Рассмотрим задачу анализа ремонта для 3-х избыточных строк и 3-х избыточных столбцов. Для покрытия ошибок через алгоритм CRESTA диаграмма потребления резервных элементов имеет 20 возможных решений. Следовательно, схема анализатора будет включать в себя 20 основных модулей. Mы разработали метод оптимизации алгоритма анализа ремонта, который приводит задачу ремонта памяти с избыточными элементами (M, N) к задаче (M – 1, N – 1). В результате уменьшается количество основных модулей и ожидается уменьшение схемы поверхности.

Для решения проблемы оптимизации алгоритм начинает использование резервных алиментов до достижения вершины (2,2) (рис. 4, б). Таким образом, на первом шаге алгоритм рассматривает задачу покрытия двух первых дефектов. Возможны следующие случаи.

● Строка – Строка (row-row)

Для ремонта оставшихся неисправностей возможны 4 случая, то есть могут быть использованы 4 параллельных и независимых модуля для ремонта оставшихся неисправностей.

● Столбец – Столбец (column-column)

Рис. 3. Диаграммa потребления резервных элементов памяти

а б

Рис. 4 Диаграммa потребления резервных элементов памяти; а – до оптимизации; б – после оптимизации

Распространяя рассуждения предыдущего случая, получаем то, что в этом случае также после первых двух шагов необходимо 4 модуля для ремонта оставшихся неисправностей.

● Строка – Столбец, Столбец – Строка (row-column, column-row)

В этом случае для ремонта оставшихся неисправностей остаются 2 избыточные строки и 2 избыточных столбца, так, что для ремонта оставшихся неисправностей может быть использован CRESTA (2,2), который содержит шесть модулей, работающих параллельно.

Таким образом, предложенный алгоритм содержит 4 + 4 + 6 = 14 модулей вместо 20-ти. Этот результат предполагает определенное сокращение в площади электронной схемы.

Результаты исследования и их обсуждение

В ходе выполнения данной работы было проведено моделирование и синтез для анализаторa bira2X2 на языке Verilog. Для описанных модулей была применена одинаковая тестовая среда (test-bench). Полученные числовые значения основных параметров представлены в таблице. Как видно из приведенных результатов, предлагаемый метод оптимизации позволяет сократить площадь анализатора до 14 %, энергопотребление снижается на 5–13 %, в зависимости от параметров памяти.

Реультаты моделирования анализатора bira_r2c2

|

Названия проекта |

Объем памяти |

Площадь (вент.) |

Частота, МГц |

Общая мощность, мкВт |

|||

|

До опт. |

После опт. |

До опт. |

После опт. |

До опт. |

После опт. |

||

|

bira256X32 |

256×32 |

875 |

812 |

1500 |

1500 |

257 |

165 |

|

bira512X16 |

512×16 |

1187 |

1025 |

1500 |

1500 |

832 |

632 |

|

bira1024X32 |

1024×32 |

1648 |

1493 |

1500 |

1450 |

1076 |

916 |

|

bira4096X64 |

4096×64 |

2954 |

2483 |

1500 |

1450 |

1355 |

1108 |

Заключение

В работе представленa методология проектирования анализаторов ремонта памяти, который, с помощью специальных диаграмм потребления, определяет и объединяет повторяющиеся части алгоритма, снижая площадь схемы анализатора в пределах 7–14 %, в зависимости от параметров памяти.

Рецензенты:

Шукурян С.К., д.ф.-м.н., профессор, старший управляющий отдела вложенного тестирования и ремонта компании «Синопсис», г. Ереван;

Казеннов Г.Г., д.т.н., профессор кафедры ПКИМС, НИУ МИЭТ, г. Зеленоград.

Библиографическая ссылка

Саргсян В.К. МЕТОДОЛОГИЯ ПРОЕКТИРОВАНИЯ ВСТРОЕННЫХ АНАЛИЗАТОРОВ РЕМОНТА ПАМЯТИ // Фундаментальные исследования. 2015. № 5-2. С. 335-339;URL: https://fundamental-research.ru/ru/article/view?id=38218 (дата обращения: 24.04.2026).